This article has been accepted for publication in IEEE Sensors Journal. This is the author's version which has not been fully edited and content may change prior to final publication. Citation information: DOI 10.1109/JSEN.2023.3289594

IEEE SENSORS JOURNAL, VOL. XX, NO. XX, MONTH X, XXXX

# Low-temperature thin film encapsulation for MEMS with silicon nitride/chromium cap

Anna Persano, Alvise Bagolini, Jacopo Iannacci, Senior Member, IEEE, David Novel, Adriana Campa, Fabio Quaranta

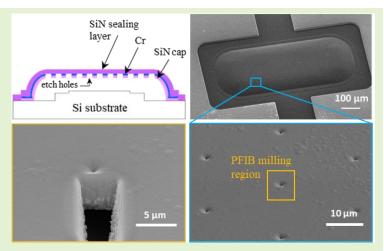

Abstract— In this work, a low-temperature fabrication process of thin film encapsulation (TFE) with silicon nitride/chromium cap is proposed for large-size (750 µm x 300 µm) packaging of microelectromechanical systems (MEMS). A FEM model was developed to evaluate the shape of TFE as a function of the residual stress and the thickness of the sealing layer, providing useful guidelines for the fabrication process. The low temperature of 200 °C, which was used in the plasma-enhanced chemical vapor deposition of the silicon nitride capping layer, allowed an organic sacrificial material to be employed for the definition of the encapsulation area. Silicon nitride/chromium (1 µm/20 nm) bilayer was demonstrated to be successful to overcome the technological limitations that affect the creation of cap holes with

Sensors Council

size of ~2 µm on high topography substrates, as in the case of MEMS. Plasma focused ion beam (PFIB) and scanning electron microscopy (SEM) techniques were used in combination to gain deeper insight into the sealing process of cap holes. Specifically, a PFIB-SEM serial section procedure was developed, resulting to be a powerful tool to directly observe the sealing profile above cap holes.

Hence, the presented results greatly contribute to overcome the main technological/reliability issues of TFE, paving the way for the widespread application of the proposed encapsulation methodology to the most used MEMS devices, as radio-frequency (RF) switches, transducers, actuators, sensors and resonators.

Index Terms— MEMS, thin film encapsulation, silicon nitride, residual stress.

#### I. INTRODUCTION

MICROELECTROMECHANICAL-SYSTEMS (MEMS)based sensors, actuators, and transducers have been pioneering various market applications and sectors for more than three decades. Starting from the first successful exploitation of inertial sensors for airbags in the automotive industry in the '90s, MEMS-based devices have known successive waves in mass-market applications, like game consoles, smartphones and, more recently, wearables [1]. In terms of numbers, MEMS technology has been employed in

This paragraph of the first footnote will contain the date on which you submitted your paper for review. This work was supported in part by the Italian Space Agency (ASI) within a project (cod. F36C18000400005) in the call: "Nuove idee per la componentistica spaziale del futuro". The author D. Novel received the patronage of the Caritro Foundation for the funding of young researchers (FLEXBOND project).

A. Persano, A. Campa, and F. Quaranta are with IMM-CNR, Institute for Microelectronics and Microsystems, National Research Council, Via Monteroni, 73100 Lecce, Italy (e-mail: anna.persano@cnr.it).

A. Bagolini, J. lannacci, and D. Novel are with SD-FBK, Center for Sensors and Devices, Fondazione Bruno Kessler, Via Sommarive 18, 38123 Povo – Trento, Italy. all the main sectors, such as consumer, automotive, industrial and telecom, reached a market volume of about 12 B\$ in 2020 with important growing rates forecasted in the next years [1]. Given this scenario, the future paradigms of 6G, Super Internet of Things (Super-IoT) and Tactile Internet (TI), will increasingly rely on smart, highly-integrated and power autonomous sensors and devices based on MEMS and nanosystems (NEMS) [2]. From a technology-related perspective, the mentioned applications pose non-trivial challenges in terms of manufacturing, integration, sensors fusions and interfacing of heterogenous technologies, along with reliability and performance stability of MEMS/NEMS devices. To this end, a pivotal role can be played by packaging solutions since they ensure proper encapsulation and protection of micromechanical devices from harmful environmental factors, while easing integration of such components within sub-systems and systems [3,4].

Thin-film encapsulation (TFE) is an alternative and attractive technique to wafer bonding for packaging of MEMS, as it helps in the reduction of the overall device thickness, seal ring area and cost due to the elimination of the cap wafer [5,6].

XXXX-XXXX © XXXX IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information. This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see https://creativecommons.org/licenses/by/4.0/ Fabrication of TFE mainly implies the following technological steps: (i) deposition of a sacrificial layer on the wafer with unreleased MEMS devices; (ii) patterning of the sacrificial layer to define the encapsulation area; (iii) deposition of the cap layer in a metal, dielectric or semiconductor material with thickness in the range 1-10  $\mu$ m; iv) patterning of the cap layer to create the matrix of etch holes; (v) removal of the sacrificial material through the etch holes; (vi) sealing.

A drawback of TFE method is the difficulty to encapsulate large-size MEMS devices, due to the low spring constant of the large and thin cap layer. To improve the robustness of TFE caps, periodic columns to support the capping structure [7] or thicker layers for capping and/or sealing [8-10] have been proposed in literature, but they generally imply difficulties in the fabrication, introduce an unnecessary increase in topography or cannot be used for all MEMS devices. A robust Ni/AlN bilayer cap has been also presented [11] for TFE of MEMS, but this solution cannot be used in situations where nickel is a contamination.

The residual stress of capping and sealing layers in TFE is an important concern to assure robustness and reliability to TFE. In fact, a thin film is desirable for sealing to reduce processing cost and time, but it might cause faulty sealing or excessive downwards bending due to the low cavity internal pressure and film residual stress. Generally, a low (< 100 MPa) tensile stress is beneficial for capping layer since voids and buckling may form in the thin film if tensile or compressive stress exceeds a critical level, either during deposition of the thin film or during use [12]. Otherwise, an overall compressive residual stress is desirable for the sealing layer to counter structure downward bending that might be generated by a tensile state and/or the difference of pressure inside and outside the encapsulation MEMS cavity.

In the fabrication of TFE a particular attention has been also devoted to the choice of the sacrificial material. The sacrificial material has to satisfy the following requirements: (i) good selectivity during the release with respect to the cap and the other structural materials, which are used in the fabrication of MEMS devices; (ii) easy deposition and patterning with a good uniformity of thickness on large areas. Inorganic materials, like silicon oxide and amorphous silicon, are generally used as sacrificial materials [7,10,11,13], but their etching requires F-based vapors that could be a serious challenge in combination with micromachining technologies for structures containing aluminum or silicon oxide. Organic sacrificial materials can be removed with an oxygen plasma etching [14,15], leaving more freedom for the choice of the capping layer material that can suit the application (optically transparent, metal capping layer, etc.). Organic materials are also suitable for process flows at low temperature (< 100°C), which are mandatory for applications when a lower thermal budget is required [16,17]. On the other hand, a hightemperature process is suitable for encapsulating MEMS devices made out of materials that can withstand high temperatures, such as silicon, poly-silicon, silicon dioxide, silicon nitride, aluminum nitride (AlN), but it may affect metal contacts and/or induce out-of-plane deformations in the suspended beams of MEMS. [18]

Another critical issue of TFE fabrication is the release time for the removal of the sacrificial material. A long release time may limit choices of cap and sacrificial layer materials because it might increase the chance that the release etch attacks the cap layer or MEMS device during the release process. Consequently, the release time should be as fast as possible to reduce this attack and to improve the throughput of the TFE process. A distribution of etch holes of  $\sim 2 \mu m$  in diameter is generally created in the cap layer to allow the release process [15,19]. In particular, the cap hole size has to be large enough to allow the complete removal of the sacrificial material in a reasonably short etching time, but the hole size has to be as small as possible to facilitate the sealing. From the technological point of view, the creation of cap holes of  $\sim 2 \mu m$  in diameter is not trivial, due to the need to perform a high-resolution lithographic process on a non-planar substrate, as in the case of MEMS.

Hence, it can be concluded that a deep investigation of materials and processes to be used for the fabrication of TFE is mandatory to solve the technological/reliability issues that still limit the widespread application of TFE to MEMS, such as the moderate thermal budget of the fabrication process, a properly tailored residual stress in the capping and sealing layers, the encapsulation of large area devices, the creation of cap holes with size suitable to achieve a fast release and a safe sealing. In particular, the trade-off between the use of a thin sealing film and the need for a perfectly sealed and sufficiently high encapsulation cavity is paramount.

In this work, a fabrication process of TFE for MEMS is developed. Section II presents the FEM model that is formulated and used prior fabrication to predict the effects on the TFE shape of the residual stress in the sealing layer made out of silicon nitride with thickness in the range 1.5-4  $\mu$ m. As described in Section III, the design and the process flow are conceived to address the technological issues that still affect TFE fabrication. Experimental results are presented and discussed in Section IV, especially those concerning the creation of cap holes, the release, and the sealing. Finally, the conclusions derived from the presented work are presented in Section V.

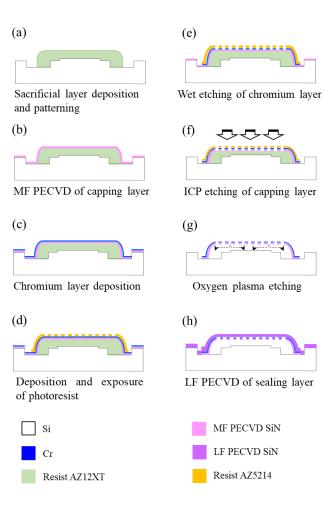

### II. FINITE ELEMENT MODEL

A finite element model (FEM) was developed, using AnsysTM software, to predict the shape of TFE as a function of sealing layer residual stress and thickness. The modelled encapsulation cavity is of 750 µm x 300 µm with a height of 20 µm, as required for the packaging of most MEMS devices. The packaging model is made of two layers with different thickness and residual stress to reproduce TFE capping and sealing layers. Silicon nitride was chosen as material for both layers since it satisfies some essential requirements in the perspective to make the packaging process suitable for industrial production, such as a good structural integrity and selectivity with respect to the sacrificial material during the chemical etching, an excellent insulation during device operation, and an optimized deposition rate in relation to the thickness to achieve. Moreover, PECVD offers the possibility to obtain silicon nitride films with controlled residual stress by changing the plasma generator frequency and gas flows [20,21]. The silicon nitride capping layer is supposed to have a

thickness of 1 µm and an ultra-low (< 10 MPa) residual tensile stress, as already reported for mixed-frequency PECVD silicon nitride films [22]. The modelled sealing material is a PECVD silicon nitride deposited at a pressure of 550 mTorr, which sets the sealed cavity's final internal pressure. A Young's modulus of 200 GPa is supposed for silicon nitride of both layers [23]. The thin chromium layer, which was used in the fabrication of the device as a hard mask, was excluded from this model, after initial simulation showed that its contribution is largely negligible due to the very limited thickness. A schematic of TFE model is reported in Fig. 1.

Fig. 1. Schematic of TFE model.

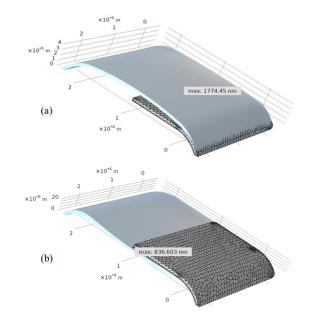

The model of one quarter of the cap was created and meshing was performed with triangle shapes, obtaining 19318 elements. Linear structural static analysis was used to obtain the height of the TFE as a function of sealing layer residual stress and thickness. A set of simulations was performed varying the sealing film thickness in the range 1.5-4  $\mu$ m and the residual stress from a highly tensile (700 MPa) to a highly compressive value (-700 MPa). Figs. 2 (a) and (b) show the effect on the TFE shape of a residual compressive stress of - 690 MPa (a) and tensile stress of 200 MPa (b) in the sealing layer, having this last a thickness of 4  $\mu$ m. An upward and a downward bending of TFE are visibly observed in the first and second cases, respectively.

Fig. 2. Bending of TFE generated by a residual compressive stress of -690 MPa (a) and a tensile stress of 200 MPa (b) in the sealing layer, having this last a thickness of 4  $\mu$ m. The TFE shapes without and with residual stress are shown in dark and blue colour, respectively. The displacement values of the TFE centre are also reported.

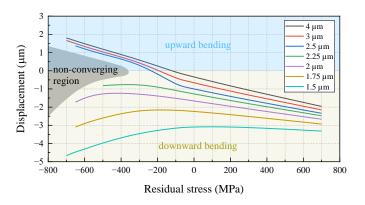

Fig. 3 shows the displacement of TFE centre as a function of the residual stress in the sealing layer, whose thickness varies in the range 1.5-4 µm. As expected, a tensile stress causes a downward displacement, which shows an increase linearly proportional to the stress value. In the case of compressive stress, a downward bending is also observed for thicknesses up to 2.25 µm. For thicknesses greater than 2.5 µm, an inversion of bending, from downward to upward, is observed. In particular, a turning point is obtained for a sealing thickness between 2.25 and 2.5 µm and a compressive stress greater than ~350 MPa: thicknesses greater than 2.5 µm are affected by an increase of the upward bending, whereas thicknesses lower than 2.25 µm exhibit an increase of downward displacement, which is caused by a negative buckling of the cap. This buckling is more pronounced at higher compressive stress values, as expected in buckling phenomena. A region of instability, where the FEM analysis does not converge, is also reported in Fig. 3. In this region, the combined effect of pressure gradient and residual stress generates an unstable equilibrium in the model.

Fig. 3. Displacement of the TFE centre as a function of residual stress and thickness of the sealing film.

Simulation results were used as guidelines to identify thickness and residual stress values in the sealing layer that are suitable to avoid significant deformations of the encapsulation structure and/or buckling phenomena. In particular, simulations show that for a sealing thickness greater than 2.5  $\mu$ m, as generally required for the complete sealing of cap holes, a compressive stress between 100-200 MPa and 700 MPa is predicted to obtain a slight (< 1.8  $\mu$ m) upward bending of TFE, which could be beneficial to counter the downward bending of TFE due to the tensile stress in the capping layer and/or to the different pressure between the inside and the outside of the encapsulation cavity.

### III. DESIGN AND PROCESS FLOW

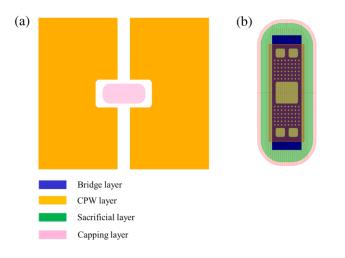

The fabrication process of TFE for MEMS is significantly influenced by the high topography of substrate, due to the presence of devices to be encapsulated. Moreover, other components are generally required for the operation of MEMS, such as the coplanar waveguides (CPWs) in the case of radio-frequency (RF) MEMS switches. These elements do not need encapsulation, but they contribute to substrate topography. In order to consider this aspect, TFE structures are designed in the central part of a CPW [Fig. 4(a)] and a beam with the same shape of those typically used in MEMS is placed inside TFE structures [Fig. 4(b)]. To exactly replicate the topography of MEMS, a uniform distribution of holes with a diameter and pitch of 10 µm is situated in the beam. The encapsulation area, which is defined by the sacrificial material [see green area in Fig. 4(b)], is of 750 µm x 300 µm with a curvature of 120 µm at the corners. The cap covering the encapsulation area has a 20 -µm -wide sealing ring [see pink area in Fig. 4(b)] and contains a uniform distribution of holes with different density and diameter. Hole diameter (D) varies in the range 2-3 µm and the percent ratio between the hole total area and the encapsulating area ranges from 1% to 4%, resulting in a minimal distance between holes (pitch) varying from 10 µm to 17 µm.

Fig. 4. (a) Design of TFE, beam, and CPW. (b) Details of TFE and encapsulated beam.

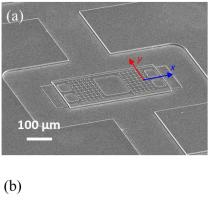

The high topography of substrate due to the presence of MEMS and CPWs was created carrying out a Bosch silicon deep reactive ion etching (DRIE) in two steps [Fig. 5(a)]. Firstly, an etching of 2.5  $\mu$ m was performed to create the beam [see blue area in Fig. 4(b)], then a second etching of 10.5  $\mu$ m was carried out to create the CPW and a rectangular shape on the beam [see orange areas in Figs. 4(a) and (b)]. Substrate profile in the directions longitudinal and transverse to the beam is sketched in Fig. 5(b) and (c), respectively.

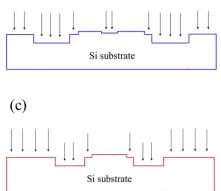

A surface micromachining approach was used to fabricate TFE structures [Figs. 6(a)-(h)]. The positive resist AZ12XT was used as sacrificial material to define the encapsulating area with a height of ~18  $\mu$ m. To this scope, the following processes were performed: spin coating at 3000 rpm, exposure to UV radiation, development, and hard-bake of 200 °C for 10 minutes to harden the sacrificial structure. A 1 - $\mu$ m -thick silicon nitride film was deposited on the sacrificial structure to form the capping layer. This layer was deposited in a mixed-frequency (MF) single process, using a coupled planar parallel

electrode Multiplex Series PECVD (Surface Technology Systems, Ltd) with an electrode diameter of 24 cm. The system is equipped with a high frequency (HF) generator at 13.56 MHz and a low frequency (LF) generator at 380 kHz. The mixed-frequency procedure consists in varying the modulation of HF and LF of RF power supply during the deposition, without changing the flows of reaction gases. For PECVD silicon nitride, it has been demonstrated [20,21] that at high frequency (13.56 MHz) the stress is compressive, whereas at low frequencies (50 kHz) the stress is tensile. Therefore, low stress dielectric layers can be deposited by stacking a tailored sequence of tensile and compressive layers deposited by HF and LF plasma, respectively. The stress of various layers compensates, providing a low stress material that is stable, also if processed at high temperature. Here, the intervals at HF and LF plasma excitation of one cycle during the deposition process are 8 s and 3 s, respectively. Due to the presence of the organic sacrificial material, a PECVD process was developed at a temperature lower than 300 °C, which is the temperature generally used for PECVD silicon nitride [19,22,24]. The operating temperature of the shower head (coil) of the machine is 250 °C, while the temperature of the chuck (platen) where the wafer is placed during the deposition process is 200 °C. The other parameters for silicon nitride deposition are 40 sccm of NH<sub>3</sub>, 40 sccm of SiH<sub>4</sub>, 1960 sccm of N<sub>2</sub>, chamber pressure of 900 mTorr, HF generator power of 30 W, and LF generator power of 20 W.

Fig. 5. (a) SEM plan view of the substrate topography after Bosch etchings. (b) and (c) Sketchs of vertical profiles of micromachined substrate along the directions longitudinal (x) and transverse (y) to the beam, respectively. The profile directions are also shown in (a).

Measurements of residual stress were performed on full wafers with the wafer curvature method, using Stoney model [25]. Measurements were carried out with a Kla-Tencor mechanical profilometer, equipped with a 2-µm diamond stylus tip. Three profiles were measured for each sample along its diameter, separated by an offset of 5 mm; the resulting stress data showed a standard deviation better than 3%. This standard deviation is valid for all stress data reported. A low tensile stress value of 2.2 MPa was measured for the silicon nitride deposited at MF, in agreement with value reported in literature [24]. Linear profiles along TFE structures were performed under the application of stylus forces in the range 4.9-490 µN.

Silicon nitride/chromium (1 µm/20 nm) bilayer caps were also deposited. Both typologies of capping layer, made of the sole silicon nitride layer and of the silicon nitride/chromium bilayer, were patterned by optical lithography to define etch holes with diameters of 2-3 µm. For this purpose, positive photoresist AZ5214 with thickness of 1.4 µm was deposited on the cap. After spin coating and exposure of the photoresist, a wet etching of 1 minute in the solution TechniEtch Cr n:1 was performed to remove the chromium inside the holes in the bilayer cap, being this process selective with respect to the used photoresist. The chromium thickness was chosen as a compromise between the needs to provide a sufficient hard masking and to avoid widening of holes during wet etching. An inductively-coupled plasma (ICP) etching was performed to open the access holes in the capping layer. The ICP etching parameters are pressure of 5 mTorr, 10 sccm of O<sub>2</sub>, 100 sccm of SF<sub>6</sub>, coil power of 300 W, platen power of 10 W, time of 210 s, and rate of 312 nm/min. An oxygen plasma etching was performed for 100 minutes in a barrel etcher to remove the sacrificial organic material inside TFE. The other parameters of barrel etching are pressure of 600 mTorr, 300 sccm of O2 with a small percentage (< 1%) of SF<sub>6</sub>, and pressure of 200 W. Adding a small amount of SF<sub>6</sub> can significantly increase the photoresist etching rate because highly reactive fluorine atoms can boost the rate of extracting hydrogen from the photoresist polymer.

A 4 -µm -thick silicon nitride layer, which was obtained at 300 °C by LF PECVD process, was used to seal TFE caps. Low-frequency PECVD silicon nitride deposited at 300 °C has been already used for this purpose [19], due to its thermal expansion compatibility with common cap materials and moisture barrier properties [26]. Here, other deposition parameters used for LF PECVD of silicon nitride are chamber pressure of 550 mTorr; 1960 sccm of N<sub>2</sub>, 40 sccm of SiH<sub>4</sub>, 20 sccm of NH<sub>3</sub>, LF generator power of 60 W, and rate of 45.5 nm/min. The residual stress measured for the sealing silicon nitride is -690 MPa. Thickness and residual stress of the sealing layer were chosen, according to previous simulations that predict a negligible  $(1-2 \mu m)$  upward bending of TFE for a sealing thickness and residual stress of 4 µm and -700 MPa, respectively (see Fig. 3).

Fig. 6. Process flow for the fabrication of TFE structures with silicon nitride/chromium bilayer cap. In the case of cap made of sole silicon nitride, the steps (c) and (e) were not performed.

# IV. RESULTS AND DISCUSSION

#### A. Creation of cap holes

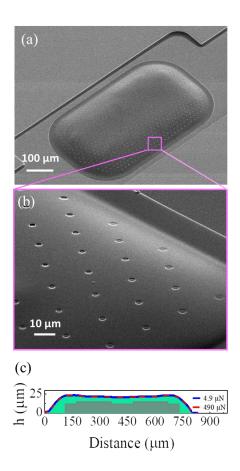

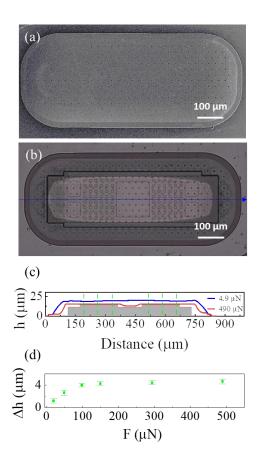

Fig. 7(a) shows a silicon nitride TFE cap after the deposition and the exposure of the photoresist for the definition of etch holes with size of 2  $\mu$ m. The cap hole pattern with the underlying sacrificial material is clearly visible in Fig. 7(b).

Fig. 7(c) shows the profilometry scans recorded along the TFE covered by the photoresist with stylus forces of 4.9  $\mu$ N and 490  $\mu$ N. The cap shows a quite flat profile with a height of 19  $\mu$ m in the centre. A downward bending of the central region of TFE cap is observed with respect to the edges, which is generated by reflow effects in the underlying photoresist during hard bake. Due to this hardening process of the sacrificial material, no variation is observed in profiles with increased stylus force.

Fig. 7. SEM images of a whole silicon nitride TFE cap (a) and of a region of the TFE cap (b), after the deposition and the exposure of the photoresist for the definition of holes with size of 2  $\mu$ m. (c) Profiles along the TFE structure after the lithographic patterning. The substrate profile is also sketched in (c).

Here, a fluorine-based ICP etching was used to create the etch holes in TFE cap. A trade-off between photoresist thickness and minimum feature size has to be found, given the limitations of optical photolithography and the selectivity of the plasma etching process. Moreover, the uniformity of the photoresist across the wafer is inevitably compromised by the high topography of the substrate, due to the presence of CPWs and sacrificial structures to be encapsulated. From several performed tests, it was found that the positive resist AZ5214 with the thickness of 1.4  $\mu$ m is the best trade-off solution to pattern TFE cap with holes of 2-3  $\mu$ m, considering the inevitable photoresist thinning in the regions of high topographical variation, which are the cap borders and corners.

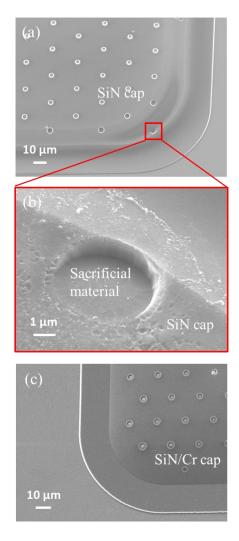

Significantly different results were obtained after ICP etching for caps made of the sole silicon nitride layer and of the silicon nitride/chromium bilayer. In the first case, a ring along the cap edge, especially at the corner, is clearly visible, which indicates an unwanted etching of silicon nitride in the regions where the photoresist is thinner [Fig. 8(a)]. In agreement with this interpretation, Fig. 8(b) shows a significant reduction of silicon nitride thickness along the edge of a hole situated at the corner of the cap. It is worth noting

that the hole in Fig. 8(b) also shows a widening effect because at the corners of encapsulation the lithographic mask is not in contact with the cap. To avoid this effect, in successive samples etch holes have not been placed at the cap corners.

Figure 8(c) shows the border and corner regions of a silicon nitride/chromium bilayer cap after the ICP etching. No ring is observed along the border and at the corner, denoting that the chromium layer effectively prevents the etching of silicon nitride in the regions where the photoresist is thinner.

Fig. 8. (a) SEM top-view of the border and corner regions of a silicon nitride cap after ICP etching. (b) High-magnification SEM image of a hole in the silicon nitride TFE cap at the corner region. (c) SEM top-view of the border and corner regions of a silicon nitride/chromium bilayer cap after ICP etching.

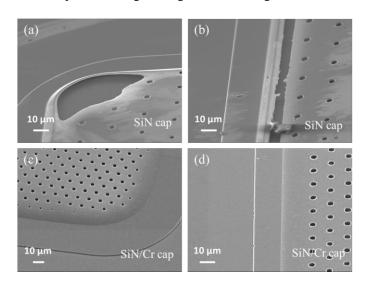

### B. Release

An oxygen plasma etching was performed in a barrel etcher to remove the sacrificial material through the etch holes of the TFE cap. Figs. 9(a) and (b) show the corner and border regions of a silicon nitride cap after the release process. Perforation of TFE cap is visible at the corner and along the border, which is caused by an unwanted ICP etching of the silicon nitride in the regions where the photoresist is thinner. Instead, no damage is observed at the corners and along the border of silicon nitride/chromium bilayer cap, as observed in Fig. 9(c) and 9(d), respectively. This result confirms the success of the thin chromium film in protecting the silicon nitride cap from damage during the ICP etching.

Fig. 9. SEM view of the corner (a) and border (b) regions of a silicon nitride cap after release. SEM views of the corner (c) and border (d) regions of a silicon nitride/chromium bilayer cap after release.

The complete removal of the sacrificial material below the TFE cap depends on the interplay between the properties of the barrel etching and the geometric parameters of cap hole distribution. Due to its pure chemical nature, the barrel etching is an isotropic process. The spherical shape of the etching front below a hole in the TFE cap can be observed in Fig. 10(a).

Figs. 10(b) and (c) show the volume below the cap in the case of incomplete and complete removal of the sacrificial material, respectively. As expected, the regions more critical for the removal of the sacrificial material are those between holes. Consequently, the size and the pitch of etch holes are determinant for the release time, which is required for the complete removal of the sacrificial material. Etch holes with a larger size are preferred for release, but these holes will hinder the efficient sealing of TFE cap. The etching is also limited by diffusion of etching species through the holes and to the etch front, and of the etch product from the etch front to the etch holes. In conclusion, the release time (*tRE*) is expected to satisfy the following formula [13]:

$$t_{RE} \ge \frac{P - D}{2X} \tag{1}$$

where *P* is the pitch between holes, *D* is the hole size and *X* is the etch rate of the sacrificial material. However, this formula can only provide a lower estimate of the expected release time. The performed etching tests started with the release of caps with larger ( $D = 3 \mu m$ ) and denser ( $P = 10 \mu m$ ) etch holes, before focusing on the release of caps with the smallest ( $D = 2 \mu m$ ) and less dense ( $P = 17 \mu m$ ) holes that is the most beneficial pattern for TFE sealing. Given the sacrificial material used here, it was found that the etching rate is 206 nm/min and the release time is 100 min for the distribution of holes with  $P = 17 \mu m$  and  $D = 2 \mu m$ . The obtained release time satisfies the condition  $t_{RE} \ge 36$  min that is given by the formula (1).

Fig. 10. SEM images of silicon nitride/chromium bilayer caps that have been intentionally broken after the oxygen plasma etching. (a) Isotropic etching front below a cap hole. (b) Residual sacrificial material between cap holes in the case of incomplete release. (c) Volume below the cap in the case of complete release.

Figure 11(a) shows the SEM image of a silicon nitride/chromium bilayer cap after the release process with  $t_{RE}$  = 100 min,  $P = 17 \mu m$  and  $D = 2 \mu m$ . Optical inspection was also performed on the same cap to check the complete removal of the sacrificial material, as silicon nitride is a transparent material [Fig. 11(b)]. Optical images show that the TFE cap was properly released, without any sacrificial residues. Figure 11(c) shows the mechanical profiles recorded for the TFE cap of Figs. 11(a) and (b) under the application of the stylus forces of 4.9  $\mu$ N to 490  $\mu$ N. Increasing the force, the cap bends due to the absence of the sacrificial material. Under the application of the highest force value, the cap results to be collapsed above the encapsulated beam, as pointed out by the

cap height of 14.5  $\mu$ m that is very close to the sum of the height of the beam (13  $\mu$ m) and the bilayer cap thickness (1.02  $\mu$ m). Consistently, the profile central concavity, having a width and depth of 100  $\mu$ m and 2.5  $\mu$ m, respectively, is perfectly conformal with the hole created in the beam with the first Bosch process step. Fig. 11(d) shows the increase of the cap deflection as a function of the applied force in 6 different points of the top surface (see green dotted lines in Fig. 11(c)) of five caps. Deflection is observed to increase with the applied force, until a saturation to the value of 4.6±0.4  $\mu$ m.

Fig. 11. SEM plan-view (a) and optical microscope image (b) of a released silicon nitride/chromium cap with holes of 2  $\mu$ m. (c) Profiles along the blue line drown in (b) under the application of the stylus forces of 4.9  $\mu$ N and 490  $\mu$ N. (d) Deflection of the TFE cap as a function of the applied stylus force, starting from the profile recorded for the lowest force of 4.9  $\mu$ N. The beam inside encapsulation is visible in (b) and the different colour in the central part of the optical image is due to the different focus for the highest central region of cap compared to border regions. The substrate profile is also sketched in (c). Deflection values in (d) are calculated in the cap points indicated by the green dotted lines in (c).

# C. Sealing

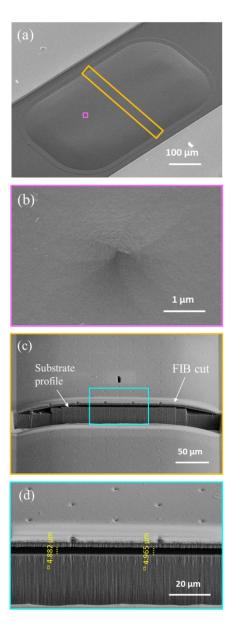

The last step in TFE fabrication is the sealing process, which was obtained by low-frequency PECVD of a 4  $-\mu$ m -thick

Fig. 12. (a) SEM image of a sealed TFE. (b) High-magnification SEM image of a sealed hole with size of 2  $\mu$ m. (c) SEM cross-sectional view of a FIB cut through the sealed TFE. (d) Zoom of the air gap between the cap and the substrate. Frames of different colour are drawn in (a) and (c) to indicate the regions magnified in (c), (b), and (d). Two measurements of the air gap inside encapsulation are also reported in (d).

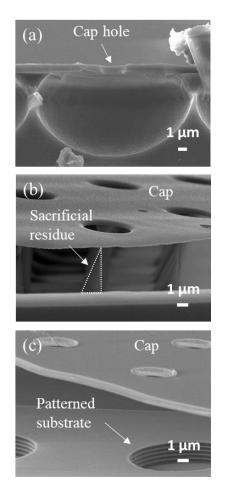

silicon nitride layer [Fig. 12(a)]. A high-resolution SEM image of a sealed 2 - $\mu$ m -sized hole is shown in Fig. 12(b). The granular morphology of the silicon nitride as well as some line features, which can be ascribed to the process of hole sealing, are observed. In order to gain more insight into the sealing process, a FIB-SEM analysis was performed with a Thermo Scientific Helios 5 Plasma FIB (PFIB) Dual Beam. FIB milling was carried out at 30 kV, with a large cut at high current close to the area of interest. This cut was made through the TFE and exposes its layered structure. The FIB milling continues with a serial sectioning at lower current in a process that resembles thinning of TEM lamellas. Figure 12(c) shows

the inside of TFE, which is observable from a typical FIB cut of the cap. The substrate profile, which was obtained with the performed Bosch etching of the silicon substrate [Fig. 5(c)], is visible. Complete removal of the sacrificial material is observed in the central region of the encapsulation cavity, which would be the region of interest for device operation. Specifically, the air gap between the encapsulated beam and the cap was extrapolated by SEM analysis [Fig. 12(d)], resulting to be  $4.94 \pm 0.05 \,\mu\text{m}$ , in agreement with profilometry measurements [Fig. 11(d)].

Similar results have been obtained for TFE with area until 900  $\mu$ m x 900  $\mu$ m. For larger areas, a proper TFE scheme is probably needed to assure the robustness of the encapsulation.

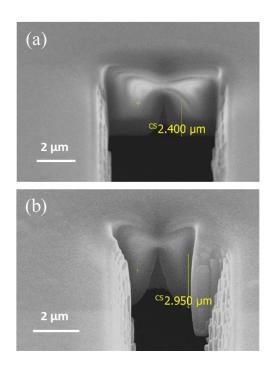

The configuration of the electronic and ionic columns of the Helios PFIB-SEM allows to perform SEM microscopy, while the ion column is milling. This process can be automated with the intermittent switching between patterning and imaging features (iSPI), after having optimized the two beam scanning parameters to minimize image shift between consecutive cross-sections. Multiple analyses were performed, with low amorphization depth thanks to Xe+ plasma [27,28]. The sequence of SEM images was later converted with FIJI platform [29] into a .gif file for visualization purposes (available in the Supporting Information). The obtained PFIB-SEM serial section procedure provides a valuable analytical tool to investigate the sealing process since, compared to the analysis of a single cross-section, it allows to directly observe the sealing profile from the border to the centre of the hole. Figs. 13(a) and (b) show the SEM images recorded when the FIB beam is cutting the hole along its maximum size, that is along its diameter of 2 µm and 2.5 µm, respectively. Under this condition, a cusp is visible in the profile of the sealing layer on top of the hole. The cusp height minus the cap thickness provides the direct measurement of the minimum material thickness required for the complete sealing of the cap hole. Cusp height measurements result to be 2.4+0.2 µm and 2.95+0.15 µm for holes with size of 2 µm and 2.5 µm, respectively. Hence, the minimal thicknesses of LF PECVD silicon nitride of ~1.4 µm and ~1.95 µm result to be required for the complete sealing of cap holes with size of 2 µm and 2.5 um, respectively. However, based on finite element simulations (see Fig. 3), buckling phenomena could occur if the silicon nitride sealing layer is thinner than 2 µm and is affected by a high compressive stress. All these aspects have to be considered in the TFE design and fabrication.

The height increase of a TFE before and after FIB cut was measured, resulting to be of ~390 nm. A simulation was performed to predict the height difference of fabricated TFE due to the increase of the internal pressure from low pressure (550 mTorr) to ambient pressure, as occurs before and after FIB perforation. The height increase is predicted to be 354 nm, pointing out that the performed FEM analysis is in good agreement with experimental results. It is worth noting that the pressure difference between the inside and the outside of the encapsulation cavity does not play a dominant role in setting the final cap height, its contribution being almost an order of magnitude less than that of residual stress.The residual deposition of silicon nitride inside encapsulation during the sealing process was investigated by SEM and atomic force microscopy (AFM). In the encapsulated area, traces of silicon nitride with a diameter of few  $\mu$ m and a height of ~100 nm were observed, only in correspondence of sealed etch holes. The presence of this residual silicon nitride has to be taken into account in the design of encapsulated devices, in order to optimize their performance.

Fig. 13. SEM images recorded during a FIB cut through the diameter of 2  $\mu$ m (a) and 2.5  $\mu$ m (b) of a sealed hole cap. The measurements of the cusp height, which is visible on top of the sealed hole, are also reported in (a) and (b).

#### V. CONCLUSION

A fabrication process for TFE of MEMS was developed, which overcomes the most critical technological issues arising from the need to obtain a thin, large-size, suspended and sealed cap.

Prior to fabrication, a FEM analysis was carried out to assess the effect of sealing layer thickness and residual stress on the shape of the encapsulation. Such predictions were followed in the fabrication process to prevent significant TFE deformations.

The silicon nitride capping layer was deposited by a mixed-frequency PECVD process at the temperature of 200 °C, allowing to use an organic sacrificial material that was easily removed by an oxygen plasma etching. Compared to the commonly used etching of sacrificial layers with aggressive and metal-corrosive vapours, the proposed technological solution leaves more flexibility with respect to materials of capping layer and device, thus widening the scope of application of the presented TFE. Caps made of the sole silicon nitride layer and of the silicon nitride/chromium bilayer were compared, demonstrating the success of the chromium film to prevent the damage of silicon nitride at the

corner and border regions during the etching for the creation of cap holes.

The volume inside sealed TFE was observed by the combined use of SEM and FIB techniques. Furthermore, a PFIB serial section procedure was developed to record SEM cross section images of the sealed cap hole during the FIB cut. A cusp-like sealing profile is observed above the hole, inferring that the minimal thicknesses of LF PECVD silicon nitride, which is required for the complete sealing of cap holes with diameter of 2  $\mu$ m and 2.5  $\mu$ m, is ~1.4  $\mu$ m and 1.95  $\mu$ m, respectively.

## ACKNOWLEDGMENT

The authors thank P. Cretì and M. C. Martucci for the technical support in the device fabrication process.

## REFERENCES

- "Status of the MEMS Industry 2021", Available online: <u>https://www.i-micronews.com/products/status-of-the-mems-industry-2021/</u>

- [2]. J. Iannacci and H. Vincent Poor, "Review and Perspectives of Micro/Nano Technologies as Key-Enablers of 6G," *IEEE Access*, vol. 10, no. 05, pp. 55428-55458, May 2022.

- [3]. S. Li, SiP-System in Package Design and Simulation, 1st ed. Hoboken, NJ, USA: Wiley, 2017, pp. 1–1477.

- [4]. J. H. Lau, C. K. Lee, C. S. Premachandran, Y. Aibin, Advanced MEMS Packaging, 1st ed. New York, NY, USA: McGraw-Hill Education, 2010, pp. 1–552.

- [5]. H. A. C. Tilmans *et al.*, "MEMS packaging and reliability: An undividable couple," *Microelectronics Reliability*, vol. 52, pp. 2228– 2234, Aug. 2012.

- [6]. A. Persano, F. Quaranta, A. Taurino, P. A. Siciliano, and J. Iannacci, "Thin film encapsulation for RF MEMS in 5G and modern telecommunication systems," *Sensors*, vol. 20, no. 7, p. 2133, Apr. 2020.

- [7]. F. Santagata, J. J. M. Zaal, V. G. Huerta, L. Mele, J. F. Creemer, and P. M. Sarro, "Mechanical design and characterization for MEMS thin film packaging," *J. Microelectromech. Syst.*, vol. 21, no. 1, pp. 100–109, Feb. 2012.

- [8]. Y. Shimooka et al., "Robust hermetic wafer level thin-film encapsulation technology for stacked MEMS/IC package," in Proc. Electron. Compon. Technol. Conf., May 2008, pp. 824–828.

- [9]. K.-L. Chen, S. Wang, J. C. Salvia, R. Melamud, R. T. Howe, and T. W. Kenny, "Wafer-level epitaxial silicon packaging for out-of plane RF MEMS resonators with integrated actuation electrodes," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 1, no. 3, pp. 310–317, Mar. 2011.

- [10]. A. B. Graham, M. W. Messana, P. G. Hartwell, J. Provine, S. Yoneoka, R. Melamud, B. Kim, R. T. Howe, and T. W. Kenny, "A method for wafer-scale encapsulation of large lateral deflection MEMS devices," *J. Microelectromech. Syst.*, vol. 19, no. 1, pp. 28–37, Feb. 2010.

- [11]. J. Sharma, J.-W. Lee, S. Merugu, N. Singh, "A Robust Bilayer Cap in Thin Film Encapsulation for MEMS Device Application," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 5, no. 7, pp. 930-937, July 2015.

- [12]. S. K. Lahiri, "Mechanical Stress Induced Void and Hillock Formations in Thin Films," in *Proc. IEEE Int. Workshop Mem. Technol. Des. Test*, August 1994, pp. 22-25.

- [13]. J.-W. Lee, J. Sharma, M.S. Narducci, S. Merugu, Z. Xiao Lin, and N. Singh, "Cavity-enhanced sacrificial layer micromachining for faster release of thin film encapsulated MEMS," *J. Micromech. Microeng.*, vol 25, pp. 065010-1-065010-8, May 2015.

- [14]. C. O'Mahony, M. Hill, Z. Olszewski, and A. Blake, "Wafer-level thinfilm encapsulation for MEMS," *Microelectron. Eng.*, vol. 86, pp. 1311– 1313, Dec. 2009.

- [15]. D. Reuter, A. Bertz, M. Nowack, T. Gessner, "Thin film encapsulation technology for harms using sacrificial CF-polymer," *Sens. Actuators A*, vol. 145–146, pp. 316–322, Nov. 2007.

- [16]. Y. Li, K. Cao, Y. fei Xiong, H. Yang, Y. Zhang, Y. Lin, B. Zhou, J. Huang, and R. Chen, "Composite Encapsulation Films with Ultrahigh

Barrier Performance for Improving the Reliability of Blue Organic Light-Emitting Diodes," *Adv. Mater. Interfaces*, vol. 7, no. 13, pp. 2000237-1-2000237-8, May 2020.

- [17]. J. Kim, J. H. Hwang, Y. W. Kwon, H. W. Bae, A. Myungchan, W. Lee, and D. Lee, "Hydrogen-assisted low-temperature plasma-enhanced chemical vapor deposition of thin film encapsulation layers for topemission organic light-emitting diodes," *Organ. Electron.* vol. 97, pp. 106261-1-106261-6, Oct. 2021.

- [18]. A. Persano, J. Iannacci, P. Siciliano, and F. Quaranta, "Out-of-plane deformation and pull-in voltage of cantilevers with residual stress gradient: experiment and modelling," *Microsyst. Technol.* vol. 25, pp. 3581–3588, Dec. 2018.

- [19]. K. D. Leedy, R. E. Strawser, R. Cortez, and J. L. (Jack) Ebel, "Thin-Film Encapsulated RF MEMS Switches," *J. Microelectromech. Syst.*, vol. 16, no. 2, pp. 304-309, Apr. 2007.

- [20]. D. Hess, "Plasma enhanced CVD: oxides, nitrides, transition metals and transition metal silicides," *J. Vac. Sci. Technol. A*, vol. 2, no. 2, pp. 244-252, Apr.-June 1984.

- [21]. A. Bagolini, A. Gaiardo, M. Crivellari, E. Demenev, R. Bartali, A. Picciotto, M. Valt, F. Ficorella, V. Guidi, and P. Bellutti, "Development of MEMS MOS gas sensors with CMOS compatible PECVD inter-metal passivation," *Sens. Actuators B: Chemical*, vol. 292, pp. 225-232, April 2019.

- [22]. A. Picciotto, A. Bagolini, P. Bellutti, and M. Boscardin, "Influence of interfaces density and thermal processes on mechanical stress of PECVD silicon nitride," *Applied Surface Science* 256, no. 1, pp. 251– 255, August 2009.

- [23]. C. A. Zorman, R. C. Roberts, and L. Chen, *MEMS Materials and Processes Handbook*, Boston, MA: Springer US, 2011.

- [24]. A. Tarraf, J. Daleiden, S. Irmer, D. Prasai, and H Hillmer, "Stress investigation of PECVD dielectric layers for advanced optical MEMS," *J. Micromech. Microeng.*, vol. 14, no. 3, pp. 317–323, Nov. 2003.

- [25]. G. G. Stoney, "The tension of metallic films deposited by electrolysis," in *Proc. R. Soc. Lond. Ser. A*, vol. 82, May 1909, pp. 172–175.

- [26]. K. Najafi, "Micropackaging technologies for integrated microsystems: Applications to MEMS and MOEMS," in *Proc. SPIE Micromachin. Microfab. Process Technol. VIII*, vol. 4979, January 2003, pp. 1–19.

- [27]. T. L. Burnett, R. Kelley, B. Winiarski, L. Contreras, M. Daly, A. Gholinia, M.G. Burke, and P.J. Withers. "Large volume serial section tomography by Xe Plasma FIB dual beam microscopy," *Ultramicroscopy* vol. 161, pp. 119-129, February 2016.

- [28]. J. Liu, R. Niu, J. Gu, M. Cabral, M. Song and X. Liao "Effect of ion irradiation introduced by focused ion-beam milling on the mechanical behaviour of sub-micron-sized samples," *Scientific reports*, vol. 10, pp. 10324-1-10324-8, June 2020.

- [29]. J. Schindelin, et al., "Fiji: an open-source platform for biological-image analysis," *Nature methods*, vol. 9, no. 7, pp. 676-682, July 2012.

A. Persano received the Laurea degree (cum laude) in Physics from the University of Lecce, Italy, in 2003 and the Ph.D. degree in Material Engineering from the University of Salento, Italy, in 2008. Since 2013, she is member of the permanent Research Staff at the Institute for Microelectronics and Microsystems of the National Research Council (IMM-CNR). Her major research interests include the electrical characterization and reliability of

MEMS in III-V and Si-based technologies for RF applications, the development of wafer-level thin-film micropackaging methodologies, and the electrical characterization of 2DEG-based GaAs photodetectors for optoelectronic applications. She has authored about 60 international scientific publications, including papers in peer-reviewed journals, conference proceedings, and book chapters. She serves as Reviewer for several international peer-reviewed science journals.

A. Bagolini graduated with a BSc Degree in physics from the University of Trento, Italy. In 2001, he was a Technologist at ITC IRST, and is now enrolled as MEMS researcher in the Micro Systems Technology group of the FBK, Kessler Foundation for Research. His main fields of activity are silicon-based transducer design, microfabrication process design and development, mechanical characterization of materials for MEMS. He

is the author of more than 100 peer reviewed publications and 2 patents.

J. lannacci (Senior Member, IEEE) was born in Bologna, Italy, in 1977. He received the MSc (Laurea) degree in electronics engineering from the University of Bologna, Italy, in 2003, and the PhD in information and telecommunications technology from the Advanced Research Center on Electronic Systems "Ercole De Castro" (ARCES) at the University of Bologna, Italy, in 2007.

He received the Habilitation as Associate Professor in Electronics from the Italian Ministry of Education, University and Research (MIUR), in 2017, and the Habilitation as Full Professor in Electronics from the Italian Ministry of University and Research (MUR), in 2021.

He worked in 2005 and 2006 as visiting researcher at the DIMES Technology Center (currently Else Kooi Lab) of the Technical University of Delft, the Netherlands, focusing on the development of innovative packaging and integration technology solutions for RF-MEMS (Radio Frequency passives in MEMS technology) devices. In 2016, he visited as seconded researcher the Fraunhofer Institute for Reliability and Microintegration IZM in Berlin, Germany, to conduct high-frequency characterization of RF-MEMS components jointly with the RF & Smart Sensor Systems Department at IZM. Since 2007, he is researcher (permanent staff) at the Center for Sensors & Devices of Fondazione Bruno Kessler, in Trento, Italy.

His research interests and experience fall in the areas of Finite Element Method (FEM) multi-physics modelling, compact (analytical) modeling, design, optimization, integration, packaging, experimental characterization and testing for reliability of MEMS and RF-MEMS devices and networks for sensors and actuators, Energy Harvesting (EH-MEMS) and telecommunication systems, with applications in the fields of 5G, Internet of Things (IoT), as well as future 6G, Tactile Internet (TI) and Super-IoT.

Dr. lannacci authored more than 130 scientific contributions, including international journal papers, conference proceedings, books, book chapters and one patent. Since 2015, he is member of the editorial board of the Springer Microsystem Technologies. He is currently associate editor of the Springer Microsystem Technologies and of Frontier in Mechanical Engineering. He was and is currently involved in several international conferences as symposium chair/co-chair, session chair, technical program committee member, international advisory board member, tutorial lecturer and invited speaker, among which the following few are mentioned: IEEE Sensors; IEEE 5GWF/FNWF; SPIE Microtechnologies; ESSCIRC-ESSDERC; ESREF; MNDCS.

D. Novel received M.S. in Materials Engineering in 2015 and PhD-Doctor Europaeus in Civil, Environmental and Mechanical Engineering in 2019, he visited Nanoforce Technology Limited and Queen Mary University of London. His research studies at Fondazione Bruno Kessler (FBK) comprise of additive manufacturing technologies for space applications and micro fabrication techniques for flexible electronics and advanced packaging solutions.

A. Campa was born in Immenstadt (Germany). Since 2017, she is member of the permanent Technician Staff at the Institute for Microelectronics and Microsystems of the National Research Council (IMM-CNR). Her major research interest is the fabrication of micro- and nano-devices in III–V semiconductor technology for sensing and optoelectronic applications. She has coauthored several peer-reviewed publications in international science journals and conference proceedings.

F. Quaranta was born in Bari (Italy). He received the degree in physics from the University of Bari in 1988. In 1994, he joined the Institute of Microelectronics and Microsystems of the National Research Council (IMM-CNR) in Lecce, Italy, becoming a permanent staff member in 1998. He is currently in charge of the scientific activities and development of the advanced micro and nano electronics device laboratory in IMM-CNR Institute in Lecce and reference person for all the activities related to opto- and micro/nano-electronics devices fabrication.

He is expert in many of the processes that can be performed in a clean room, related to micro-, nano- and optoelectronics devices fabrication in III–V semiconductor technology and for MEMS: optical photolithography, plasma enhanced chemical vapor deposition (PECVD) of silicon nitride and silicon oxide, reactive ion etching, high density plasma etching (ICP) with both chlorine and fluorine chemistry, physical vapor depositions (sputtering, evaporation).

He has authored more than 100 papers in peer-reviewed international science journal, 2 patents and many international conference proceedings.